## www.ramauniversity.ac.in

## FACULTY OF ENGINEERING AND TECHNOLOGY MEC-022 Lecture - 05

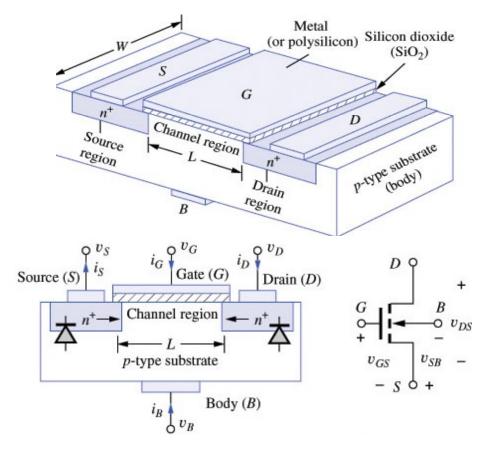

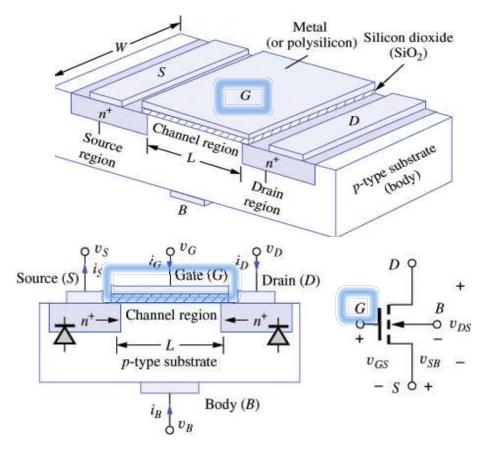

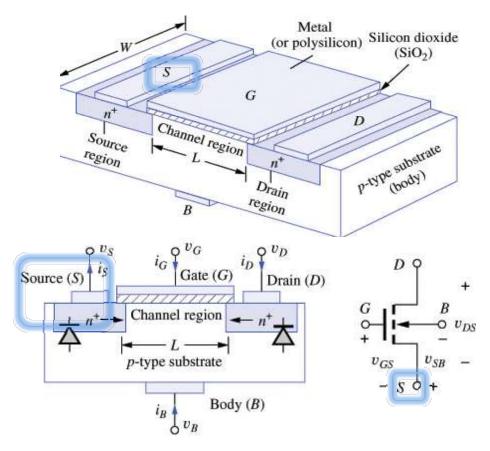

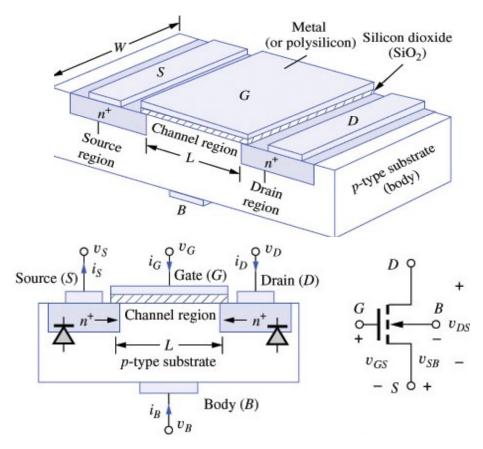

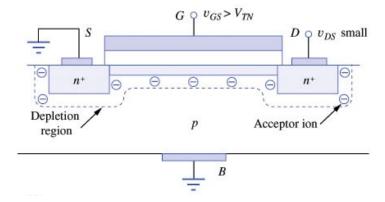

4 device terminals:

Gate(G)

4 device terminals:

Gate(G) Drain(D), Source(S)

• 4 device terminals:

Gate(G) Drain(D), Source(S) Body(B).

- Source and drain regions form *pn* junctions with substrate.

- $v_{SB'} = v_S v_B$ ,  $v_{DS} = v_D v_S$  and  $v_{GS}$ =  $v_G - v_S$  are always positive during normal operation.

- v<sub>B</sub> <= v<sub>D</sub> and v<sub>B</sub> <= v<sub>S</sub>, to keep pn junctions reverse biased.

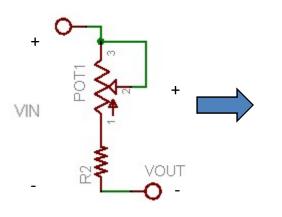

## NMOS Transistor and Variable Resistor

- A transistor is a three (or four) terminal device, in which one terminal controls the voltage or current between other two terminals

- In certain way it is similar to a variable resistor, in which the movement of the middle terminal controls the voltage.

## NMOS Transistor: Qualitative Behavior @ $v_{DS}$ =0

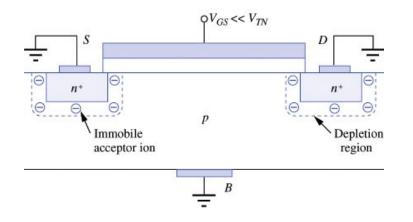

V<sub>GS</sub><<V<sub>TN</sub> (V<sub>GS</sub><0): Two back to back reverse biased pn junctions btw S and D. Only small leakage current flows.